„Liczba tranzystorów w układzie scalonym (procesorze) zwiększa się w kolejnych latach zgodnie z trendem wykładniczym – podwaja się w dwunastomiesięcznych okresach.” Tak mówi Prawo Moore’a. Czytelnicy jednak wielokrotnie pisali, że „co to za prawo, które przestało się sprawdzać”.

Ograniczenia współczesnej technologii

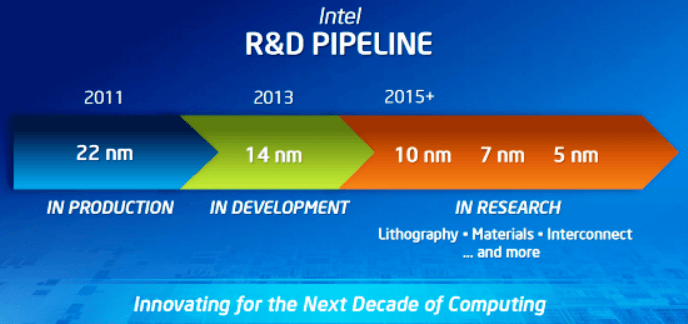

Chcąc zrozumieć problem rozwoju procesorów i nagłego zatrzymania wzrostu mocy obliczeniowej, trzeba uświadomić sobie, że „Prawo Moore’a” wynika z obserwacji, jest prawem empirycznym, a nie uniwersalnym. Gordon Moore, jeden z założycieli Intela, w 1965 roku zauważył tą prawidłowość, która utrzymywała się przez kolejne dziesiątki lat. Z czasem jednak okresy, w których moc podwajała się wydłużyły się do 24 miesięcy. Dzięki czemu taki szybki rozwój był w ogóle możliwy? Jednym z głównych powodów jest stosowanie coraz mniejszych elementów w procesie produkcyjnym procesorów. W latach 90-tych używano technologii o litografii 500 nanometrów, podczas gdy współcześnie przeważają technologie 45 nm, 32 nm (Sandy Bridge), 22 nm (Haswell) i już wkrótce 14 nm (Broadwell).

Trzeba jednak zdawać sobie sprawę, że rozmiary te nie mogą zmniejszać się bez końca z uwagi na twarde ograniczenia fizyki klasycznej. Wartością graniczną będzie oczywiście rozmiar atomów (dla przykładu – atom krzemu ma średnicę 0,24 nm), a przejście z krzemu na grafen czy german również nie pozwoli na minimalizowanie litografii w nieskończoność – nawet w przypadku, gdyby pojedyncza ścieżka procesora miała grubość jednego atomu. Kolejnym ograniczeniem jest też prędkość światła, która wraz z fizycznymi rozmiarami płytki warunkuje maksymalną możliwą szybkość przesyłania informacji.

Od wielu lat zapowiada się, że Prawo Moore’a przestanie (przestało?) obowiązywać. Sam Gordon Moore, w roku 2006 powiedział, że za kilka lat jego „prawo” nie będzie miało zastosowania właśnie z uwagi na ograniczenia fizyki klasycznej. Producenci pokonują jednak kolejne granice i już teraz wiemy, że w 2016-2017 najprawdopodobniej uda się zejść poniżej 10 nm. Nie rozwiązuje to jednak problemu, a jedynie go odracza. Wkrótce i tak napotkamy ścianę limitów fizycznych i co wtedy? Możliwości producentów nie kończą się tak szybko. Pozostaje jeszcze optymalizacja programowa i zmiana architektury. Nie zmienia to „czystej” mocy obliczeniowej, ale pomaga oszukać ograniczenia i zwiększyć realną wydajność w praktycznych zastosowaniach. Dodawanie kolejnych rdzeni pomaga, ale też nie jest optymalnym rozwiązaniem – nie wszystkie procesy i zadania da się zrównoleglać (na poziomie bitów, rozkazów, danych i zadań), a całą wojnę na rdzenie czasami można ironicznie sprowadzić do pytania: „Wolałbyś osiem Fiatów czy jednego Bentleya?”.

Problematyczne jest też zjawisko wycieku (prąd upływu, „leakage”), które wzmaga się wraz z wzrostem częstotliwości procesora. Jest to niepożądany efekt kwantowy, polegający na tunelowaniu elektronów przez warstwę izolatora. Duże prądy upływu zwiększają pobór energii i mogą doprowadzić nawet do całkowitego uszkodzenia układu. Zjawisko wycieku jest obecnie jednym z głównych czynników limitujących maksymalne częstotliwości pracy procesorów. Na chwilę obecna wygląda na to, że nawet jeśli zmienimy architekturę i będziemy używać innych materiałów, problemu tego nie przeskoczymy.

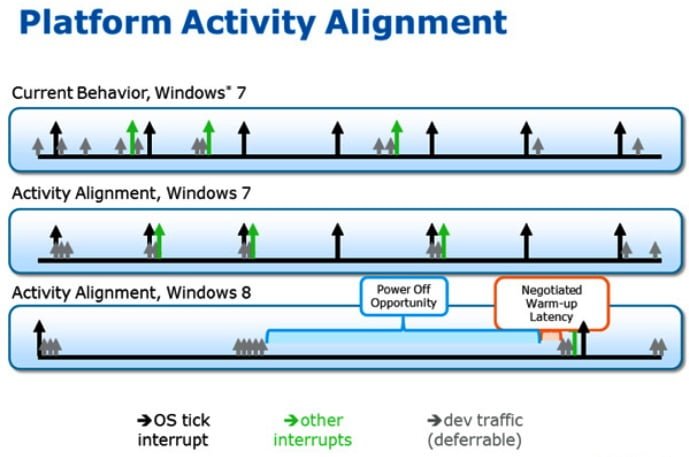

Zacznijmy od optymalizacji programowej czyli software’u. Dopracowanie wykonywania rozkazów, zrównoleglania i sterowników może przełożyć się na wzrost odczuwalnej mocy obliczeniowej. Doskonałym przykładem zastosowania tych rozwiązań jest architektura Haswell, która opiera się na tym samym procesie litograficznym (22 nm) co poprzednia generacja Ivy Bridge. Mimo tej samej wielkości ścieżek, udało się podwyższyć moc obliczeniową o 10-20% redukując przy tym pobór prądu o 30-40%. Jednym z trików było zbalansowanie obciążenia CPU i układanie rozkazów w grupy odpalane synchronicznie w równych odstępach czasu, w opozycji do asynchronicznego wykonywania rozkazów niezależnie, po otrzymaniu sygnałów z wybranych peryferiów. Do tego jednak nie wystarczy technologia procesora – potrzebny będzie kompatybilny system operacyjny. Intel pracował blisko z Microsoftem i Apple, żeby ich OS-y w pełni wykorzystywały możliwości CPU i GPU w sposób optymalny. W przyszłości pojawią się kolejne rozwiązania związane między innymi z Panel Self Refresh, czyli odświeżaniem obrazu monitora. Firmy pracują nad tym, żeby w sytuacjach „statycznych” (czytanie tekstu, oglądanie zdjęcia) nie odświeżać go 60 razy na sekundę. Wszystkie te drobne kroczki składają się na jedną całość, ale dalej nie rozwiązują problemu ściany, z którą wkrótce musimy się zderzyć.

A może zmienić architekturę współczesnych komputerów zachowując paradygmat obliczeniowy maszyny Turinga (bo każdy współczesny komputer to maszyna Turinga)? Jest to bardzo ciekawa koncepcja i to nie tylko teoretyczna. W HP Labs, laboratorium badawczym Hewlett Packarda, od jakiegoś czasu pracuje się nad komputerem „The Machine”, który zmienia podejście do projektowania maszyn liczących. Współcześnie przetwarzanie danych w komputerach i innych urządzeniach polega na wykonywaniu prostych operacji binarnych oraz przenoszenia bloków danych między poszczególnymi rodzajami pamięci – od L1 i L2 w procesorze, poprzez pamięć RAM, aż do pamięci wewnętrznej urządzeń czy zewnętrznych nośników danych. Dlaczego aż tyle rodzajów pamięci? W telegraficznym skrócie – duża pamięć jest wolna, szybka pamięć jest mała. A do tego: szybka-duża pamięć jest potwornie droga i trudna do produkowania na masową skalę. W związku z tym pamięć w komputerach jest hierarchizowana – tam gdzie potrzeba dużej szybkości (blisko procesora) używa się superszybkiej pamięci rzędu pojedynczych megabajtów, potem mamy dość szybki RAM (rzędu kilku GB), dyski SSD zwykle (do ok. 1 TB) i dyski HDD i nośniki zewnętrzne o pojemności wielu terabajtów.

Segmentacja ta ma oczywisty sens z przyczyn ekonomicznych i technologicznych, ale w ogromnym stopniu spowalnia działanie komputerów. Szacuje się, że 90% czasu procesora wykorzystuje się nie na znaczące zadania obliczeniowe, a na przenoszenie bloków danych z jednej pamięci do drugiej. Czy jest na to jakiś sposób? The Machine od HP ma wykorzystywać pamięć bazującą na memrystorach, czyli rezystorach z pamięcią, które mogą przechowywać jeden bit informacji i pozwalają na budowę procesorów znacznie mniejszych niż obecnie. Użyte zostaną też bardzo szybkie fotoniczne łącza systemowe, zarówno dla podzespołów wewnętrznych, jak i urządzeń zewnętrznych. Całość ma korzystać z szybkiej pamięci uniwersalnej, bez podziału na RAM czy przestrzeń dyskową. Takie rozwiązanie mogłoby znacznie zoptymalizować i przyspieszyć działanie urządzeń opartych na takiej architekturze i odroczyć zderzenie ze ścianą na kolejne kilka lat, jednak problem ograniczeń fizyki klasycznej dalej pozostaje. Czy istnieje jakieś wyjście z tej sytuacji?